Multiplexer

Multiplexer

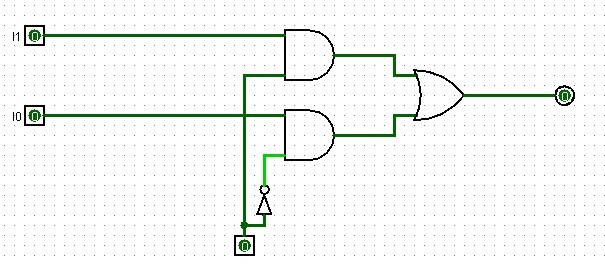

Dalla mappa di Karnaugh viene fuori U=I0S'+I1S

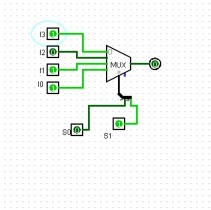

Se volessimo lavorare con m ingressi ci servirà un multiplexer con 2^n ingressi, dove n è il minor numero naturale per cui 2^n>=m. Vale a dire che se ho 5 ingressi userò un multiplexer con 8 ingressi e tre linee di selezione in quanto 2^2=4<5, 2^3=8>5 dunque un multiplexer con 2 linee di selezione non è sufficiente per selezionare tra 5 ingressi e il minor n per cui è verificata la relazione è n=3. Vediamo ora l'esempio con 4 ingressi che avrà di conseguenza 2 linee di selezione.

In questa tabella di verità ridotta ogni riga i rappresenta una situazione in cui tutti gli ingressi Im per cui m è diverso da i siano variabili "don't care". Otteniamo la funzione booleana U=I0S1'S0' + I1S1'S0 + I2S1SO' + I3S1S0

Ricavare l'espressione booleana di un multiplexer

Considero compreso il funzionamento del multiplexer pertanto d'ora in poi rappresenteremo i MUX con il simbolo nell'immagine qua sotto.

Il multiplexer può essere usato come generatore di funzioni. Prendiamo la tabella di verità di una rete combinatoria a caso per fare un esempio.

Nel caso della porta AND collegata all'ingresso I1 vogliamo in uscita I1 quanto i bit di selezione valgono 01 per tanto negheremo solo S1 in ingresso alla porta in modo da ottenere 11 in ingresso alla porta AND.

Ripetendo ricorsivamente questo procedimento arriviamo allo schema presentato precedentemente per il multiplexer 4-1.

Il procedimento appena descritto è l'implementazione fisica della funzione mk descritta nel paragrafo "Ricavare la funzione booleana di un multiplexer" in cui usavamo la definizione di mk per sapere quali bit negare per ogni porta AND.