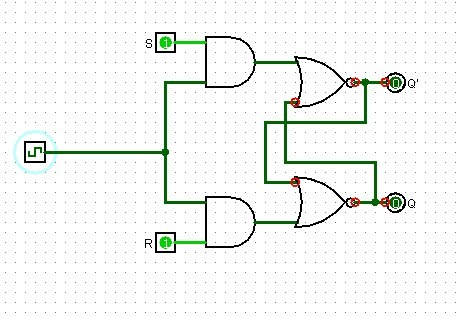

Latch

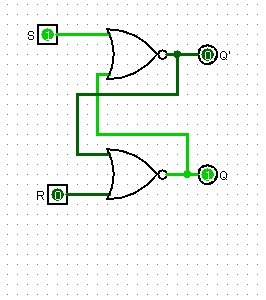

Per comprendere il Latch non proveremo a ragionare su come ottenerlo ma partiremo dal Latch e analizzandolo ne studieremo il funzionamento.

Ora abbiamo Q(t+1)=(Q'(t)+R)'=((S+Q(t))'+R)'=(S+Q(t))R'

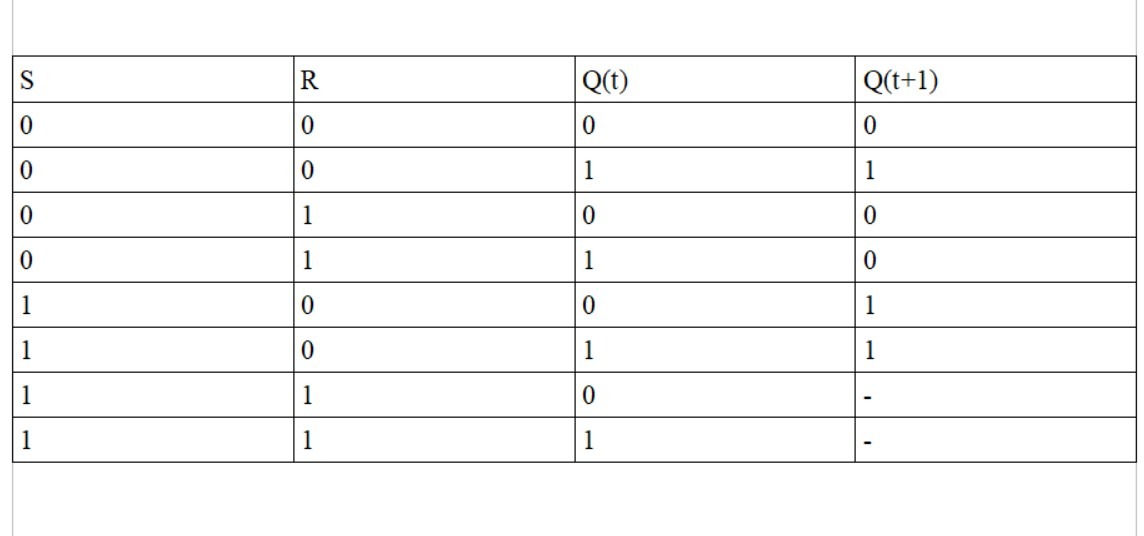

Tramite questa formula possiamo compilare la tabella di verità del Latch

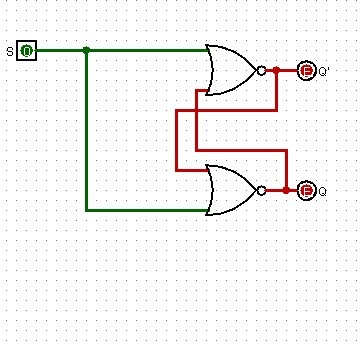

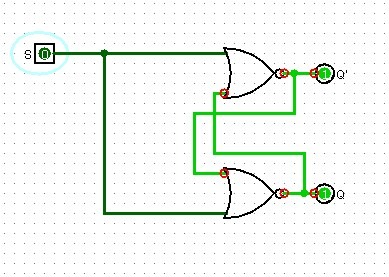

Per ora S=R= 0 e sia Q' che Q sono ancora nulli, proviamo ad azionare il Latch S-R per la prima volta ponendo S=R=1

Ora S valeva 1 e sia Q che che Q' erano stabili con valore nullo in ingresso alla porta NOR dunque tutto è andato liscio e siamo entrati nella configurazione non ammessa. Ora facendo tornare S=R=0 ci aspettiamo Q(t+1)=Q(t) come risulta nella tabella di verità ma una volta aggiornati Q(t+1) e Q(t+1)' rientreranno in ingresso alle porte NOR pur se non cambiamo il valore di S. Nella porta NOR Q(t) viene sommato con 0 (in quanto S=R=0) e poi viene negato dunque di volta in volta il segnale Q(t) entrerà nella porta NOR e verrà semplicemente negato. Il risultato e che passando S=R=1 a S=R=0 siamo entrati in una situazione dove le uscite vengono negate di continuo variando da 0 a 1 e viceversa per causa della retroazione.

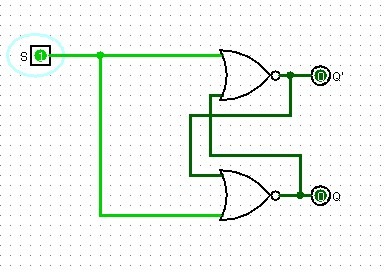

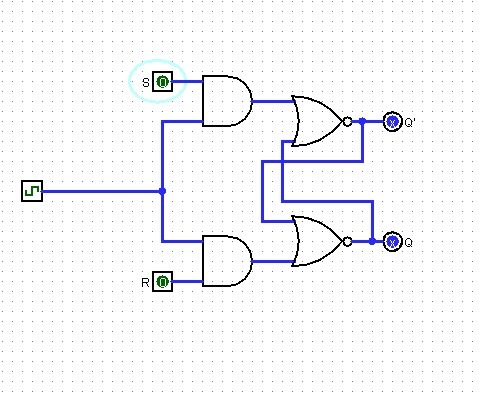

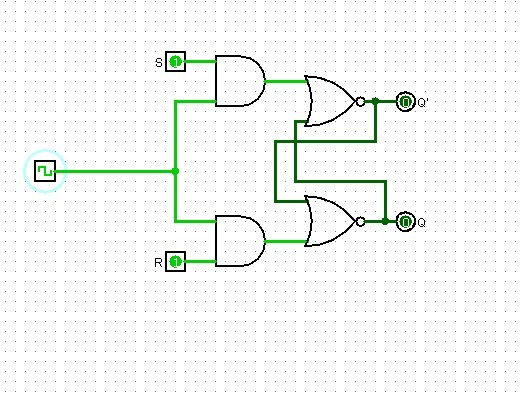

In questo caso le uscite cambiano solo durante gli intervalli di tempo in cui il clock è alto, la configurazione 1 1 è ancora proibita (genera un oscillazione delle uscite) infatti impostando 11 con il clock basso

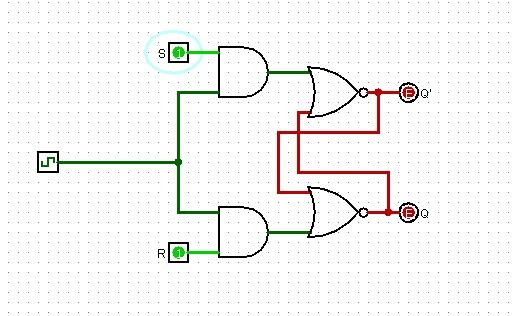

e alzando il clock entriamo nella configurazione non ammessa in cui come abbiamo detto Q'=Q.

La configurazione non ammessa è tale in quanto la situazione Q=Q' causa l'indeterminazione dello stato successivo infatti al prossimo colpo di clock noteremo l'effetto con l'oscillazione delle uscite

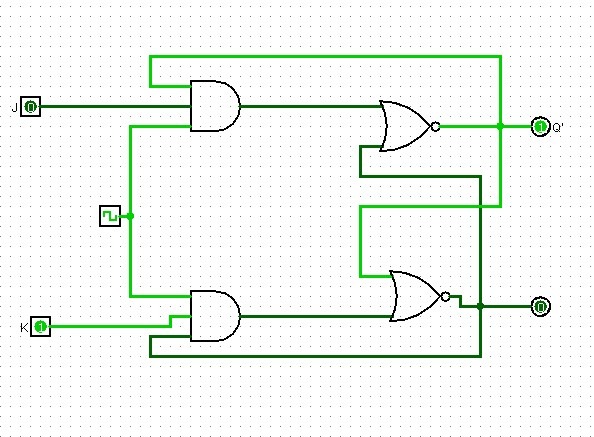

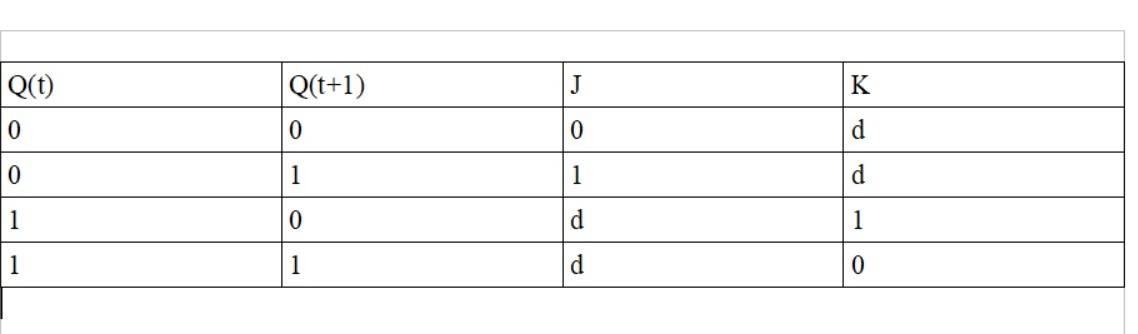

Latch D e T

Vengono ottenuti entrambi a partire dal JK collegando gli ingressi,

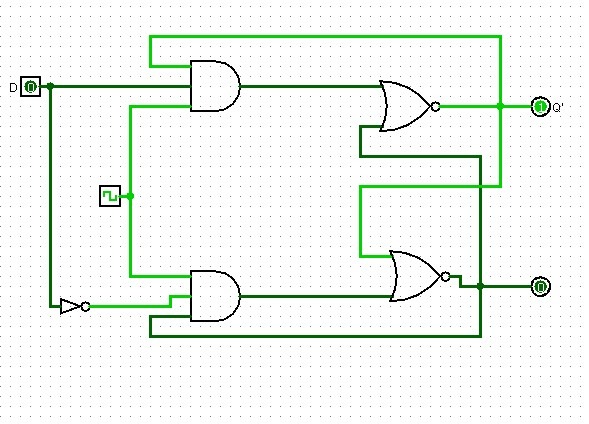

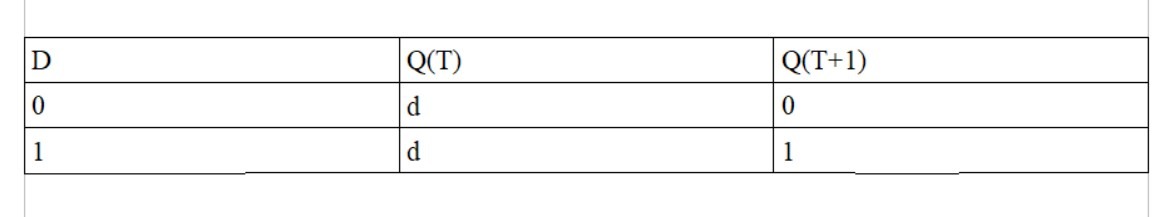

-nel caso del Latch D l'ingresso è D=J=K' dunque lo stesso ingresso viene mandato sia a J che a K ma viene negato in K,

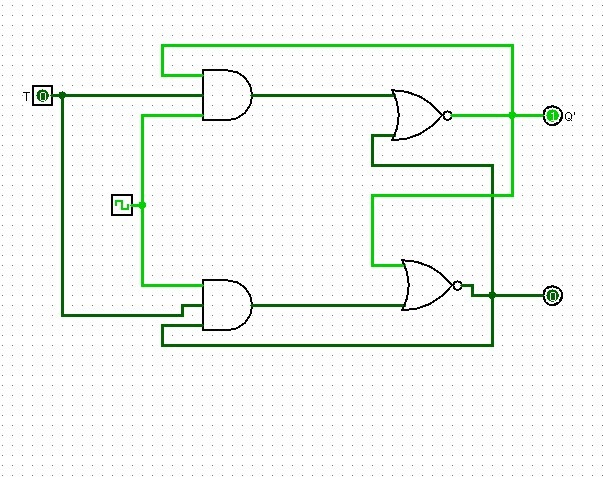

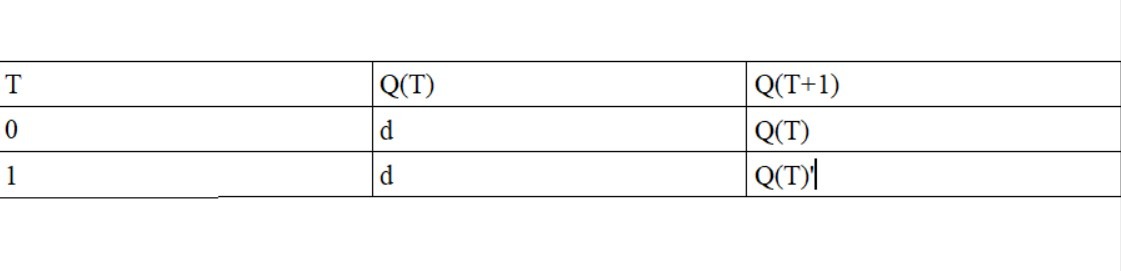

-nel caso del Latch T abbiamo T=J=K quindi semplicemente lo stesso ingresso viene collegato sia a J che a K

Vediamo qui sotto gli schemi e le tabelle di verità